Al decir que una computadora es más rápida o lenta que otra, el concepto de CPI (ciclos por instrucción) cobra relevancia, ya que puede influir en el significado de velocidad según las operaciones que se deseen ejecutar en ella

Por empezar, una persona no especialista podría tomar como referencia la velocidad con la que ejecuta un programa. Mientras que el director de un centro de cálculo, responsable de supervisar y gestionar todas las operaciones relacionadas con la infraestructura de IT en una organización, diría que la computadora más rápida es aquella que completa más tareas en una hora.

Así, un concepto tan simple puede dar lugar a dos interpretaciones distintas: para el usuario de la computadora, rapidez es reducir al mínimo el tiempo de respuesta o latencia. Para el profesional TI, productividad de los procesadores.

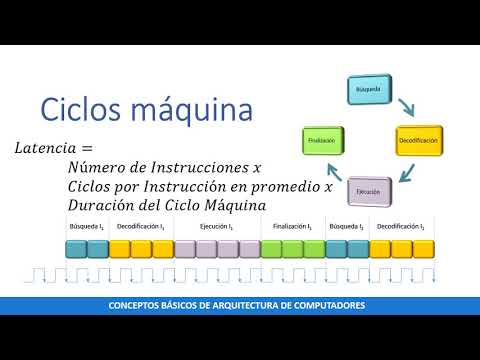

Por lo general, las computadoras cuentan con un reloj que trabaja a una frecuencia constante a través de eventos que llamamos ciclos o frecuencias de reloj. De esta manera, si nosotros contamos con la cantidad de ciclos de reloj que utiliza una computadora y con el número de instrucciones que le fue dado, podemos llegar a obtener el CPI, la cantidad de ciclos por instrucción.

Índice de temas

Introducción a los ciclos por instrucción (CPI)

Los ciclos por instrucción son métricas utilizadas en el campo de la arquitectura de computadoras para medir el rendimiento del procesador. Representa el número promedio de frecuencias de reloj que se requiere para ejecutar una instrucción de un programa.

Si el CPI es bajo, quiere decir que el procesador es más eficiente, debido a que cada instrucción se ejecuta en menos ciclos de reloj. Por otro lado, un CPI alto indica una menor eficiencia, porque está mostrando que se requieren más frecuencias para ejecutar cada instrucción.

Esto se trabaja dentro del ámbito del diseño de arquitecturas de procesadores, el cual debe siempre tender a mejorar y ser más avanzado. De hecho, los diseñadores de procesadores buscan constantemente reducir el CPI para aumentar el rendimiento y la eficiencia energética de los dispositivos informáticos.

Historia y evolución de los CPI

La historia y evolución de los CPI fueron de la mano con el desarrollo de la arquitectura de computadoras y el progreso en la eficiencia de los procesadores a lo largo del tiempo.

Primeras computadoras

En la década de 1950, cuando se daban los primeros pasos de computación electrónica, los componentes básicos de las máquinas eran válvulas termoiónicas, también conocidas como tubos de vacío.

Estas máquinas estaban hechas para la ejecución de instrucciones simples y cada instrucción requería varios ciclos de reloj para completarse. Por ende, durante este período, los CPI eran generalmente altos, debido a que los procesadores y las arquitecturas eran aún muy básicas.

Transición a transistores

Ya en 1960, con la invención del transistor, las computadoras comenzaron a volverse más pequeñas, rápidas y confiables.

La introducción de la lógica transistor-transistor (TTL) y de los primeros circuitos integrados permitieron que se logre reducir el tiempo de ejecución de las instrucciones. De esa manera, los CPI comenzaron a disminuir progresivamente a medida que la tecnología mejoraba.

Era de los microprocesadores

Para 1970, llegó la invención del microprocesador, implementada por Federico Faggin, un empleado de Intel que trabajaba en el diseño del Intel 4004, lo que marcó el hito más importante de la década en materia de computación.

Los microprocesadores facilitan que se completen múltiples funciones de una computadora en un solo chip. Es así como se pudo alcanzar un mayor rendimiento y una menor latencia en la ejecución de instrucciones.

Durante esta época, los fabricantes de microprocesadores compitieron para reducir el CPI tanto como fuera posible, mejorando la arquitectura interna y el funcionamiento de los diseños.

Multicore y paralelismo

No hace falta mencionar el gran avance que hubo en materia de computación desde la década del 90 en adelante.

Con la llegada de los procesadores multinúcleo y el aumento del paralelismo a nivel de instrucción, se realizaron esfuerzos para mejorar el trabajo de los procesadores, y se logró la explotación de tareas simultáneas y el perfeccionamiento de la ejecución de instrucciones en múltiples núcleos.

En la actualidad, procesadores como los de la generación Raptor Lake de Intel o los Phoenix, Zen 4 de AMD disponen de un menor número de núcleos en su CPU y son mucho más eficientes en materia de rendimiento, aunque demuestren un ligero descenso en sus resultados de IPC.

Desarrollo actual de los CPI

El dispositivo distribuye las instrucciones a cada núcleo según su demanda, lo cual permite una ejecución más rápida y reduce tiempos de espera.

Los procesadores Intel® Core™ de 13a Generación son un ejemplo de utilización de arquitecturas híbridas en la actualidad.

Conceptos fundamentales de los CPI

Los CPI son una medida de rendimiento. Principalmente, describen la cantidad de operaciones básicas que puede realizar una CPU en un lapso determinado e indican cuántas frecuencias de reloj se necesitan para completar una instrucción.

Para entenderlos mejor, definiremos una serie de conceptos fundamentales que giran en torno a estas métricas.

Instrucción

Se trata de una operación básica que puede ser ejecutada por la CPU como, por ejemplo, las operaciones aritméticas (como sumar o restar), las operaciones lógicas (como AND u OR), las transferencias de datos (como cargar o almacenar en memoria) o el control de flujo (como saltar a una dirección de memoria específica). En definitiva, se trata de una orden simple que la CPU puede entender y realizar.

Ciclo de reloj

Por otro lado, otro concepto fundamental de un CPI es el ciclo de reloj. Hablamos de la unidad básica de tiempo de un sistema computacional. Durante cada ciclo de reloj, la CPU ejecuta una parte de una instrucción o una serie de instrucciones.

Velocidad de reloj

Es la velocidad a la que la CPU ejecuta los ciclos de reloj. Se mide en hercios (Hz) y representa con qué frecuencia la CPU es capaz de completar un ciclo de reloj.

Pipeline

Para profudnizar un poco más, debemos hablar de un pipeline. Se trata de una técnica que se usa en el diseño de las CPU para mejorar el rendimiento al permitir que múltiples instrucciones se ejecuten simultáneamente en diferentes etapas de un ciclo de instrucción. El pipeline divide el proceso de ejecución de una instrucción en varias etapas: decodificar, ejecutar y escribir resultados.

Factores que afectan a los CPI

Los ciclos por instrucción pueden ser afectados por varios factores. Tal como hemos mencionado, es importante trabajar sobre su optimización si lo que buscamos es que nuestro procesador funcione de la mejor manera.

Microarquitectura

Particularmente, el rendimiento de los microprocesadores, contenidos en un único chip semiconductor, es afectado por tres factores: la microarquitectura, la frecuencia de reloj y las instrucciones.

En ese sentido, la microarquitectura, que trabaja sobre el diseño interno de un procesador a nivel de circuitos y componentes individuales, impacta de forma directa en la eficiencia del procesador porque de ella depende cuántos ciclos de reloj serán necesarios para la ejecución de una instrucción.

Memoria y acceso a los datos

Para completar las instrucciones, es necesario que la CPU tenga la suficiente memoria y un fácil acceso a los datos. Tengamos en cuenta que acceder, tanto a la memoria principal como a la caché, puede llevar varias frecuencias de reloj. Por ende, si esto no está trabajado de la manera indicada, el CPI podría aumentar considerablemente.

Tamaño y estructura de la caché

Uno de los objetivos principales de la caché es reducir el tiempo de acceso a los datos y a las instrucciones para mejorar el rendimiento del sistema.

De hecho, está ubicada entre la CPU y la memoria principal (RAM), de modo que actúa como un puente entre ellos. Es por ello que, cuando la computadora necesita acceder a datos o instrucciones, el primer lugar al que recurre es la caché.

Si los datos o instrucciones están presentes allí (lo que se conoce como “acertar en caché”), se puede hacer uso de ellos rápidamente, y así reducir el tiempo de espera. Como contracara, si se produce un fallo de caché, la CPU debe ir en búsqueda de los datos a la memoria principal, lo cual lleva más tiempo.

En ese sentido, si se logra obtener un buen diseño de caché, se puede reducir la cantidad de veces que se intenta acceder a los datos a través de la memoria principal. Esto hace que se optimice el número de ciclos de reloj requeridos para completar una instrucción.

Métodos de medición de CPI

Los ciclos por instrucción (CPI) se calculan al dividir el número total de frecuencias de reloj con el número total de instrucciones ejecutadas. Por lo tanto, para medir los CPI, antes que nada, es necesario contar con estos dos datos para poder llevar a cabo la matemática. La fórmula, entonces, sería la siguiente:

CPI = Número total de ciclos de reloj / Número total de instrucciones ejecutadas

Poder calcular el CPI promedio de todo el programa te ayudará a conocer la eficiencia de la ejecución de instrucciones en tu sistema y así saber si hay que trabajar sobre la optimización del rendimiento. Sin embargo, lo cierto es que el número de ciclos por instrucción solo nos puede proveer una visión parcial, por lo que es el tiempo de ejecución la única medida realmente objetiva.

Cómo calcular el CPI

Por ejemplo, imaginá que ejecutás un programa en tu procesador y observás que el número total de frecuencias es de 500.000 y el número total de instrucciones ejecutadas es de 100.000. Para calcular el CPI, simplemente dividí los ciclos de reloj entre las instrucciones:

Este resultado indica que, en promedio, cada instrucción necesita 5 ciclos de reloj para completarse. Si tu objetivo es mejorar la eficiencia, este número te ofrece un punto de referencia. Por ejemplo, un CPI más bajo podría indicar que el procesador ejecuta instrucciones de manera más eficiente, mientras que un CPI más alto podría sugerir la necesidad de optimización en el código o en el hardware.

Hoy en día existen otras maneras de medir el CPI de una CPU de manera automática. Es el caso de algunos procesadores modernos que, a través de contadores de rendimiento integrados, pueden registrar el número de ciclos de reloj y el número de instrucciones ejecutadas, llegando directamente al CPI.

En ese sentido, otros métodos, muy efectivos para la medición de CPI, son los de añadir un código adicional en el desarrollo de software y el de simulación.

Código adicional

Es posible dejar predeterminado este cálculo en el desarrollo de software, cuando se lleva a cabo la instrumentación del código, a través de uno adicional que pueda registrar la cantidad de instrucciones ejecutadas y, lógicamente, el número de frecuencias de reloj utilizadas.

Sin embargo, hay que tener cuidado con esta técnica de código adicional debido a que puede introducir algún nivel de sobrecarga en la ejecución del programa. Para evitar esto, se debe ser muy cuidadoso al seleccionar los puntos de instrumentación para minimizar cualquier impacto en el funcionamiento.

Simulación

Este método se realiza en el diseño del hardware. Consiste en llevar a cabo una simulación de ejecución de un modelo del procesador y registrar el número de ciclos de reloj y el número de instrucciones ejecutadas durante la misma. De esa manera, sin tener que usar un hardware físico, se puede alcanzar el CPI.

CPI en procesadores RISC

La Universidad Complutense de Madrid (UCM) define a los RISC como una arquitectura de procesadores diseñada para maximizar el rendimiento mediante instrucciones simples, lo que permite tiempos de ejecución bajos y un CPI ideal cercano a 1. Esta arquitectura optimiza el CPI al simplificar las instrucciones, lo cual permite, en algunos casos, ejecutar cada una en un solo ciclo de reloj. Para calcular el CPI en un sistema RISC, se aplica la siguiente fórmula:

Así, si un programa tiene 300 instrucciones con un CPI de 1 y 200 instrucciones de carga con un CPI de 2, el CPI promedio se calcula de la siguiente manera:

Optimización de CPI

El objetivo final de cualquier profesional de IT que se dedique a trabajar con procesadores de CPU es reducir el tiempo de respuesta y, por consiguiente, lograr que la máquina sea más rápida. Para ellos, tal como hemos marcado, optimizar el CPI, es decir, bajar la cantidad de ciclos por reloj que tarda un procesador en ejecutar una instrucción, es uno de los desafíos de este campo. A continuación, enumeramos algunas estrategias para abordar esta problemática.

Pipeline profundo

Recordemos que un pipeline es una técnica utilizada en el diseño de procesadores para mejorar su rendimiento, y que logre ejecutar múltiples instrucciones simultáneamente en diferentes etapas de procesamiento.

Pensémoslo de la siguiente manera: en una línea de ensamblaje de una fábrica, cada trabajador realiza una tarea específica sobre una parte de la pieza a fabricar antes de pasarla al siguiente trabajador. En la misma línea, un pipeline divide la ejecución de una instrucción en varias etapas, como buscar la instrucción, decodificarla, ejecutarla y escribir los resultados. Cada etapa se realiza en un ciclo de reloj diferente.

El beneficio del pipeline es que, a través de él, múltiples instrucciones están en diferentes etapas de procesamiento al mismo tiempo. Así aumenta la velocidad de ejecución total de las instrucciones. En lugar de esperar a que una instrucción se complete antes de comenzar con la siguiente, el pipeline comienza a procesar la siguiente instrucción mientras aún se completan las etapas anteriores para las instrucciones anteriores.

Es por ello que una manera de optimizar el CPI es a través de la utilización de esta herramienta que logra que aumente el grado de paralelismo en la ejecución de instrucciones. Es así como se puede reducir el CPI debido a que un mayor número de instrucciones se realizan simultáneamente en diferentes etapas del pipeline.

Predicción de saltos

Cuando una CPU encuentra una instrucción de salto condicional, por lo general debe esperar hasta que se resuelva la misma para determinar qué instrucción será la que se ejecutará. Esto causa un retraso en la ejecución del código, ya que la CPU podría haber utilizado ese tiempo para ejecutar otras instrucciones.

Para evitar esto, la predicción de saltos es una herramienta muy útil que intenta anticipar si un salto condicional será tomado (se ejecutará la instrucción de salto) o no tomado (seguirá la ejecución secuencial). Para hacer esto, la CPU utiliza diferentes técnicas como, por ejemplo

- Predicción estática

- Predicción dinámica

- Predicción basada en el hardware

En relación al CPI, si se mejora la precisión de las técnicas de predicción de saltos, se reducirá el número de penalizaciones de ciclos de reloj asociadas con los saltos condicionales que no estén bien predichos.

Optimización del código

Una de las tareas de diseño que pueden parecer lógicas, pero que hacen una gran diferencia, es la manera de escribir los códigos. Si se logran eliminar los códigos redundantes, se usan los algoritmos adecuados y, en línea con el apartado anterior, se minimizan los saltos condicionales, será posible reducir el número de instrucciones necesarias para realizar una tarea, reduciendo así el CPI.

Caché

Si bien ya habíamos destacado la importancia del tamaño y de la estructura de la caché, vale la pena volver sobre este punto porque es fundamental para la optimización del CPI. Mejorar el diseño y la configuración reduce los tiempos de acceso a los datos e instrucciones, y de ingreso a la memoria principal.

Aplicaciones y casos de uso de los CPI

Los ciclos por instrucción se aplican en la evaluación, en el diseño y en la mejora del rendimiento de los procesadores.

Herramienta de evaluación

Uno de los grandes desafíos de los profesionales de IT es lograr optimizar el rendimiento de los procesadores y, por ende, llegar a diseñar computadoras más rápidas. El CPI es una unidad de medida cuyo objetivo es determinar cuántos ciclos de reloj se necesitan para completar una instrucción.

De ese modo, podemos decir que es una herramienta de medición y evaluación del rendimiento de un procesador. Un CPI bajo nos muestra que el procesador puede ejecutar más instrucciones en menos frecuencias de reloj, lo que se traduce en un mejor funcionamiento.

Perfeccionamiento

Sin embargo, los ciclos por instrucción también pueden aplicarse, no solo para evaluar, sino también para mejorar el rendimiento del procesador. Por ejemplo, en un procesador segmentado, se puede iniciar una nueva orden cada ciclo de reloj para explotar el paralelismo a nivel de instrucción.

CPI en el gaming

Al momento de armar una computadora especializada para gaming, los fanáticos de los videojuegos suelen preguntarse acerca de cuántos núcleos necesita su procesador para correr el juego a una velocidad moderada. En general, la mejor opción son las CPU de 4 núcleos, pero cada caso puede variar, ya que las exigencias en los títulos más recientes pueden ser mucho más altas.

En ese sentido, una PC gamer necesita al menos un procesador con 2 núcleos, pero puede extenderse a 4 núcleos y 8 hilos. Sin embargo, el CPI también es un factor a considerar en una computadora gamer, ya que afecta directamente la velocidad de procesamiento de las instrucciones en el CPU, lo cual repercute en el rendimiento general de los juegos.

Un procesador con menor CPI puede ejecutar más instrucciones por segundo, lo cual es crucial para mantener altas tasas de frames per second (FPS) y minimizar la latencia. De esta forma, la experiencia de juego es más fluida y los tiempos de respuesta más rápidos. Incluso, los jugadores pueden elegir una calidad gráfica más alta y apreciar mejor la artística del producto.

Diseño

Por último, los ciclos por instrucción son importantes en el diseño mismo de los procesadores. El objetivo es minimizar el CPI tanto como sea posible para mejorar el rendimiento lo más posible.

Esto se logra mediante la implementación de técnicas de diseño que optimizan el flujo de ejecución de instrucciones por segundo. A su vez, también se trabaja con herramientas que reducen las dependencias de datos, como una caché eficiente, u otras que minimizan los cuellos de botella y maximizan el uso de los recursos de hardware disponibles, como las unidades funcionales.

Desafíos y futuro de los CPI

Muchos de los ámbitos de nuestra vida cotidiana y también del mundo empresarial se ven atravesados por un claro crecimiento exponencial de la tecnología. Lo cierto es que, en el sector de IT, las innovaciones avanzan con mucha más velocidad que en otros ámbitos, por lo cual los profesionales deben mantenerse capacitados permanentemente. En este apartado hablaremos sobre el futuro de los ciclos por instrucción.

Ciberseguridad

Con el aumento de actividad nefasta, como el malware y las violaciones de datos, las empresas de tecnología están trabajando arduamente para reforzar sus herramientas de ciberseguridad. En ese sentido, es importante diseñar computadoras que puedan resistir a distintos tipos de ataques.

Los sistemas informáticos eficientes y rápidos pueden ser más resistentes a ciertos tipos de ataques. En otras palabras, un sistema con un CPI bajo puede ser capaz de detectar y mitigar ataques de denegación de servicios de una mejor manera al mantener la capacidad de procesamiento disponible para responder a la carga adicional generada por el ataque.

Brecha de habilidades

Según la investigación de CompTIA, una organización sin fines de lucro de mucho renombre en el campo de la tecnología, el 93% de los empleadores informa que existe una brecha general de habilidades en sus profesionales de IT. Esto se traduce en la práctica como una disparidad entre los conjuntos de habilidades deseadas y las existentes.

Será, entonces, un desafío formar profesionales que puedan satisfacer la demanda que existe hoy en las empresas de este ámbito.

Conclusiones de la importancia del CPI

En este artículo analizamos la importancia del CPI en la evaluación y la medición del rendimiento tanto de los microprocesadores como de los procesadores. Como planteamos al principio, vulgarmente oímos que una computadora es más rápida que otra, y ahora entendemos y sabemos por qué se da esa situación técnicamente.

De este modo, podemos responder que una computadora será más rápida si logra realizar una mayor cantidad de tareas en una hora. Y el rendimiento del procesador será más óptimo cada vez que se ejecuten instrucciones por segundo en la menor cantidad de ciclos por reloj mediante un CPI bajo.

Pero, a su vez, hemos hecho hincapié en que no solo se trata de evaluar el rendimiento y nada más. También existe el desafío de bajar la latencia y alcanzar tiempos de respuesta más rápidos.

Por último, también mencionamos otros factores que afectan a los ciclos por instrucción, como el tamaño de la caché en lo que refiere al acceso a los datos o el uso de pipelines para lograr que se ejecuten varias instrucciones al mismo tiempo.

Artículo publicado originalmente en 15 Abr 2024